## NEW TOPOLOGY OF THE GaAs NON-LINEAR TRANSMISSION LINE (NLTL) USING MICROSTRIP LINE TECHNOLOGY

Salamh, D. and Linton, D.

The Queen's University of Belfast

The Department of Electrical and Electronic Engineering

Ashby Building, Stranmillis Road

Belfast, BT9 5AH, N Ireland, UK

Tel :+44+(0)1232 245133 Ext. 4089 Fax : +44+(0)1232 667023

e-mail : d.linton@ee.qub.ac.uk

### ABSTRACT

*A novel NLTL is designed using microstrip as an alternative to the coplanar wave guide (CPW) approach which has the advantage of reduced chip size and cost. A frequency multiplier has been designed with the number of sections optimized for power output using harmonic balance simulation. The large and small signal models of the 4\*75  $\mu\text{m}$  GaAs schottky diode which is used in the design are verified using S-parameters and large signal measurements.*

### INTRODUCTION

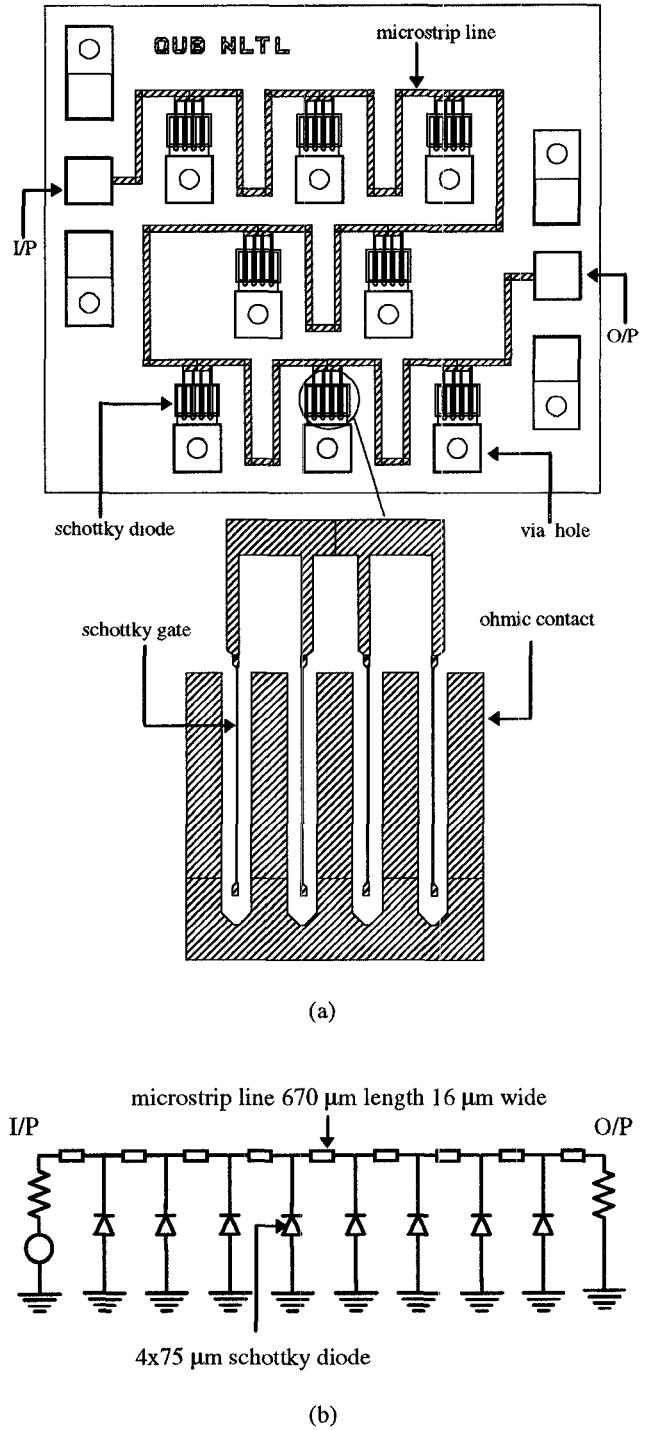

The NLTL is a monolithic circuit which typically consists of CPW connected in shunt with reverse bias schottky diodes acting as voltage variable capacitors[1],[2]. The primary application of the NLTL is in sampling circuits where it is used as a harmonic and pulse generator[2]. The performance of the NLTL is determined by the cut off frequency of the schottky diode and the skin effect losses[1]. To function properly in a NLTL the schottky diode should have small series resistance and a highly nonlinear CV characteristics. High non-linearity of the schottky diode can be achieved by using an exponentially graded doping profile[3]. Pulse signals can be generated by tapering exponentially the per section cutoff frequency[2],[4]. CPW is commonly used in the

NLTL with the advantage that both signal and ground metalization are on the same plane which makes diode grounding very easy. The disadvantage of the CPW is that it occupies significant GaAs MMIC real estate and consequently has high cost. In this paper the technology of the microstrip line and via holes is utilized. The advantage of using microstrip line is that a zigzag path is easily realized to reduce the chip size however a via hole is needed to ground each diode. The GMMT model for the via hole (valid up to 20 GHz) is used in the simulation.

### DESIGN CONSIDERATION

The 4\*75  $\mu\text{m}$  GaAs schottky diode is selected from the GMMT F20 MMIC process which has the following capacitance voltage characteristics (GMMT model)[5]

$$c_j(v) = \frac{0.377}{(1 - v/1.1)^{0.76}} \quad (1)$$

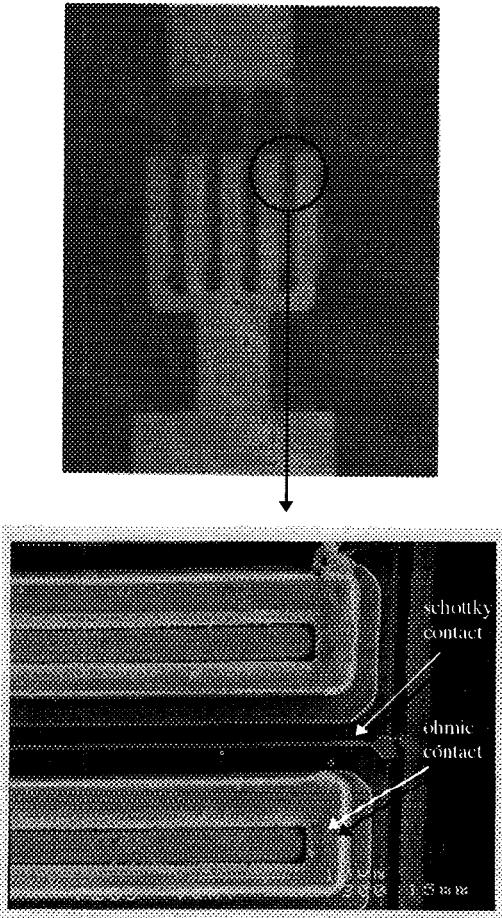

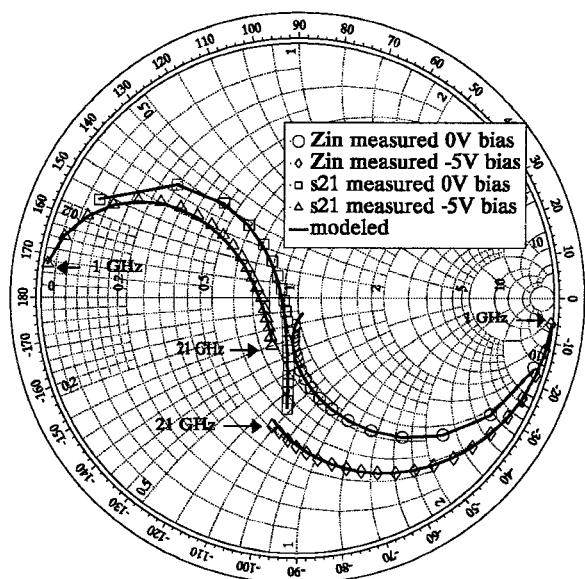

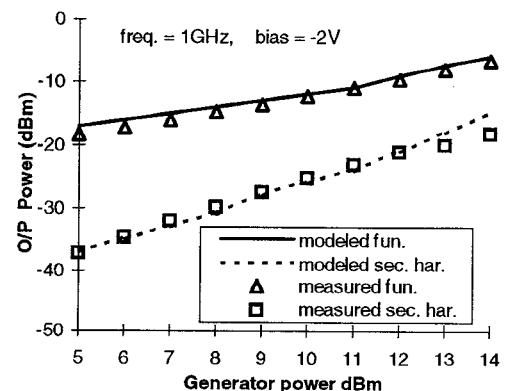

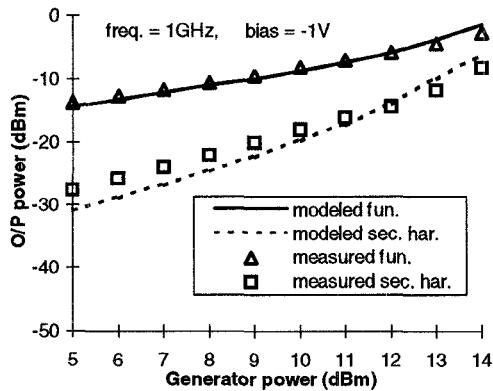

The 4\*75  $\mu\text{m}$  schottky diode fabricated using the GMMT foundry is pictured in figure 1. S-parameter measurements were performed for the range of bias points (0, -8V) to verify the GMMT model. Figure 2 shows the measured and simulated (GMMT model) S-parameters for the 0,-5V bias points were in good agreement. The measured and modeled fundamental and second harmonic are shown in figures 3,4 for bias points -2,-1V. To assure good transmission the large

WE

3F

signal input impedance( $Z_l$ )should be equal to  $50\Omega$  where[2]

$$Z_l = \sqrt{\frac{L_o}{C_o + C_l}} \quad (2)$$

$L_o, C_o$  are the per section inductance and capacitance of the microstrip line.  $C_l$  is the large signal capacitance of the diode which is given by

$$C_l = C_{coupling} + \frac{1}{v_{high} - v_{low}} \int_{v_{low}}^{v_{high}} C_j(v) dv \quad (3)$$

$C_l$  is computed to be  $0.15$  pF. The diode large signal capacitance should dominate over the microstrip line capacitance, this requires that  $Z_o \geq 75\Omega$  [2],  $Z_o$  is set to  $100\Omega$  which corresponds to a microstrip line width of  $16\mu\text{m}$  (computed using the GMMT model). The length

**Figure 1** Photograph of the  $4*75\mu\text{m}$  Schottky diode (GMMT foundry).

per section of the microstrip line is designed to be  $670\mu\text{m}$  to realize a  $50\Omega$  large signal input impedance. The microstrip line is bent by  $90^\circ$  as shown in figure 5 in order to compress the chip size. The effect of  $90^\circ$  bends and the tee junctions is taken into account using frequency dependent discontinuity models.

**Figure 2** Measured and modeled transmission coefficient ( $S_{21}$ ) and input impedance ( $Z_{in}$ , normalized by  $50\Omega$ ) for the  $4*75\mu\text{m}$  schottky diode, the frequency range is (1-21 Ghz).

**Figure 3** Measured and modeled output fundamental and second harmonic versus the generator power in dBm for  $-2\text{V}$  bias.

## SIMULATION RESULTS

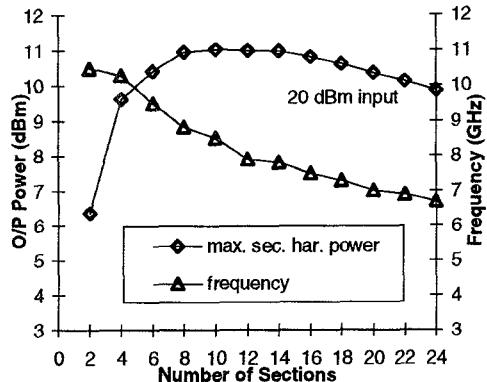

The electrical model of the designed structure is constructed using the GMMT models of the individual components (microstrip lines, corners, tee junctions, via holes and schottky diodes). The MDS harmonic balance simulator is used to run the simulation. Figure 6 shows the maximum second order harmonic power as a function of the number of sections for 20 dBm input power with a -2.5V bias. In figure 6 as the number of sections is increased the maximum second order harmonic power increases up to 8 sections beyond that the maximum second order harmonic power begins to decrease slowly.

Figure 4 Measured and modeled output fundamental and second harmonic versus the generator power in dBm for -1V bias.

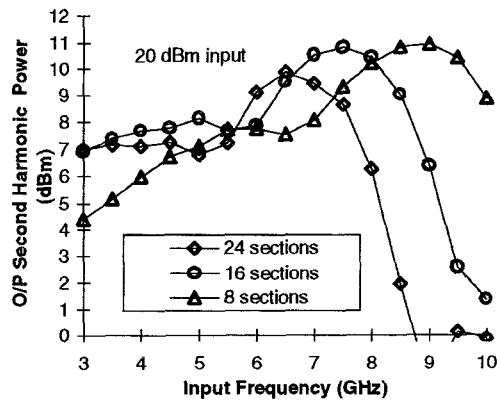

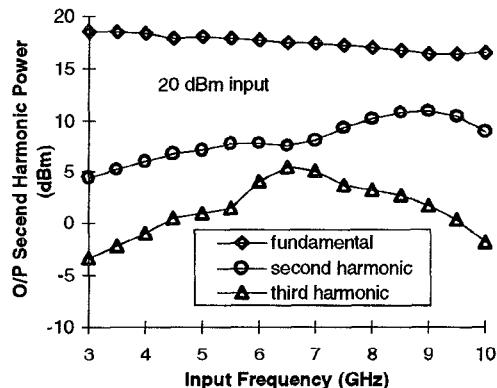

This occurs because after 8 sections the power transferred from the fundamental to the second harmonic becomes less than the power lost through the NLTL. Larger maximum second order harmonic power could be achieved by decreasing the losses and increasing the number of sections. Figure 7 shows a comparison of results for 8,16,24 section NLTLs. As the number of sections becomes larger the cut off frequency begins to decrease and the power curve becomes more flattened. Figure 8 shows the output power of the fundamental, second and third harmonics as a function of the input frequency for 20 dBm input signal power, these

results are similar to the results obtained by Rodwell [2] for a CPW based NLTL.

Figure 5 (a) Layout of the designed NLTL chip (b) Schematic diagram.

**Figure 6** Simulated maximum second harmonic power and the corresponding frequency versus number of sections.

**Figure 7** Simulated second harmonic output power versus frequency for 8, 16, 24 section NLTL.

**Figure 8** Simulated fundamental, second and third harmonics power versus frequency for 20 dBm input power (8 sections)

## CONCLUSION

Via holes and microstrip line technology are used as an alternative to CPW in the construction of the NLTL. A NLTL with compressed chip size has been designed and simulated based on the new technology. The number of sections has been optimized using electrical models based on harmonic balance simulation.

## ACKNOWLEDGMENT

The authors acknowledge the assistance of Dr. M. Darvishzadeh (RAL UK) who provided MMIC schottky diodes from the GMMT F20 process under the Eurochip program. This work is supported by ORS and ASAII.

## REFERENCES

- [1] Salamh, D. and Linton, D., "Skin Effect Modelling of the Non-linear Transmission line", Conference Proceedings-European Microwave Conference, Bologna, Italy, September 1995, pp.1138-1141.

- [2] Rodwell, M., Allen, S., Ruai, Y., Case, M., Bhattacharya, U., Reddy, M., Carman, E., Kamegawa, M., Konishi, Y., Pusl, J., and Pullela, R., "Active and Non-linear Wave Propagation Devices in Ultrafast Electronics and Optoelectronics," July 1994, Proc. IEEE, Vol. 82, No. 7, pp. 1037-1059.

- [3] Rodwell, M., Kamegawa, M., Ruai, Y., Case, M., Carman, E., and Giboney, K., "GaAs Non-linear Transmission Lines for Picosecond Pulse Generation and Millimeter-Wave Sampling," July 1991 IEEE Trans. MTT, Vol. 39, No. 7, pp. 1194-1204.

- [4] Case, M., Kamegawa, M., Ruai, Y. and Rodwell, M., "Impulse compression using soliton effects in a monolithic GaAs circuit," January 1991, Appl. Phys. Lett., Vol. 58, No. 2, pp. 173-175.

- [5] Dieudonne, J., Adelseck, B., Schmegner, K., Rittmeyer, R., Colquhoun, A., "Technology Related Design of Monolithic Millimeter-Wave Schottky Diode Mixers," July 1992, IEEE Trans MTT, Vol. 40, No. 7, pp. 1466-147